2021-12-06

-

Burn Bootloader

-

AVR fuses

-

avrdudedirect programming-

export hex and listing

-

1. AVR fuses

The ATtiny85, and many other AVR parts, has three bytes of special EEPROM called "fuses" and an additional byte holding only two bits called the lock bits. Program code cannot read or write to these bytes, only an external programmer.

The three fuses and their constituent bits are described in the datasheet, section §20.2 Fuse Bytes starting on page 148.

Term "unprogrammed" translates to a bit value of 1.

Therefore, "programmed" means a 0, which may be confusing when reading English descriptions of the fuses.

1.1. Fuse Extended Byte efuse

Only one bit of functionality:

efuse[0] — SELFPRGEN

-

Enable self-programming (program can change EEPROM and Flash).

-

Default: 1 (disabled)

1.2. Fuse High Byte hfuse

-

7 -

RSTDISBL- disable external reset (default 1, enabled) -

6 -

DWEN- enable DebugWire (default 1, disabled) -

5 -

SPIEN- enable serial program and data download (default 0, enabled) -

4 -

WDTON- Watchdog timer always on (default 1, NOT always on) -

3 -

EESAVE- EEPROM preserved during chip erase (default 1, also erased) -

2,1,0 -

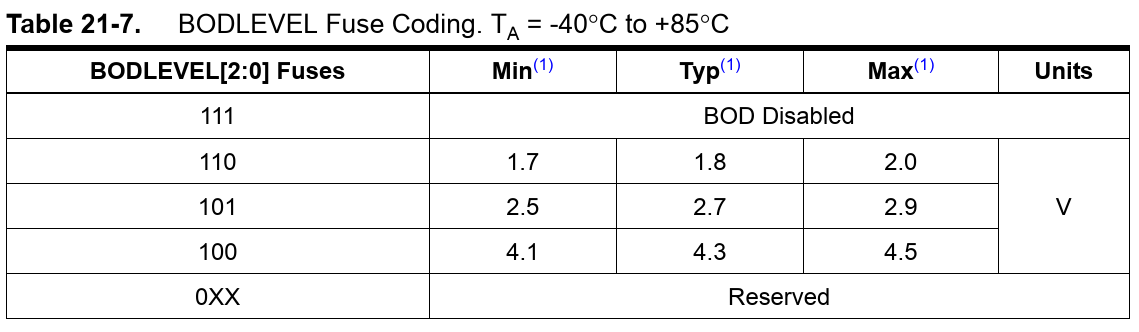

BODLEVEL[2:0]- Brown-out detector voltage (default111)

Brown-out detector circuit holds the chip in RESET until the power supply voltage is above the configured threshold. Disabled by default, but a useful feature to ensure that your power supply voltage is large enough to ensure proper system operation, especially when battery-powered.

1.3. Fuse Low Byte lfuse

Clock configuration. Remember, these settings are NOT accessible from the program code.

-

7 -

CLKDIV8- enable Clock divided by 8 (default 0, YES /8) -

6 -

CKOUT- enable Clock output (default 1, no output) -

5,4 -

SUT[1:0]- Startup time setting (default10) -

3,2,1,0 -

CKSEL[3:0]- Clock source (default0010)

CLKDIV8 affects the initial setting of the CLKPS[3:0] bits in the CLKPR clock prescaler register.

Program code can change the clock prescaler after startup.

CKOUT makes the CLKO pin output the current clock, useful for clocking other devices and having the ATtiny85 be the clock source for those parts.

SUT[1:0] allows changing the time to wait for the internal RC oscillator clock to become stable.

Table 6-7 has some advice.

CKSEL[3:0] are the most relevant and important of the fuse bits!

Unfortunately, there isn’t a nice table that summarizes all of the 16 possible combinations :(

Section §6.2.7 on page 30 describes the "as-received" clock setup for a brand new ATtiny85.

-

Clock source:

-

Frequency:

-

Divider:

-

-> resulting system clock frequency:

Go back and see where the CLKDIV8 affects the CLKPR register.

2. ATTinyCore package for Arduino IDE

This package includes all of the configuration needed for programming the ATtiny85 and others in the ATtiny series using the Arduino IDE platform and framework.

GitHub repository: https://github.com/SpenceKonde/ATTinyCore

Add the following to your File -> Preferences -> Additional Boards Manager URLs list:

-

http://drazzy.com/package_drazzy.com_index.json