1. Key terms

- sequencing elements

-

Circuits which enfoce a sequence between past - current - next data (book uses "tokens")

- timing

-

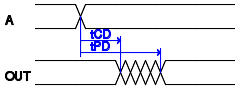

Time is everything! Figures use arrows to show cause→effect relationships between edges.

- static circuit

-

Circuit with no clock such as combinational logic gates.

- static storage

-

Latch or flip-flop that will hold its value indefinitely.

- dynamic storage

-

Latch of flip-flop that maintains its value for a short time before it needs refreshed. Usually as the charge on a capacitor which will leak.

- latch

-

Circuit with a state that holds its current output and a state where the circuit passes the input signal immediately to the output. The full name is usually level-sensitive transparent latch.

-

Positive latch is transparent when the clock is high and holds when the clock is low.

-

Negative latch holds when the clock is high and is transparent when the clock is low.

-

- flip-flop

-

Circuit which captures the state of the input at a clock edge and holds that value at its output until the next event.

-

positive / rising edge-triggered

-

negative / falling edge-triggered

-

2. Timing definitions

3. References and Tools

WaveDrom is a tool to draw timing diagrams. WaveDrom Editor allows editing and real-time preview of the code.